Vaya al Contenido

Regreso al contenido

Radiación y FPGAs para aplicaciones espaciales

BLOG > Lógica programable

Desarrollo FPGA para aplicaciones espaciales_

Radiación y partículas de alta energía

A diferencia de la mayoría de las aplicaciones en la superficie terrestre, las aplicaciones espaciales se encuentran sometidas a una radiación ionizante elevada. Esta radiación es emitida por partículas de alta energía, y es causante de errores en los sistemas electrónicos. Dependiendo del origen de las partículas, la radiación a considerar puede dividirse en tres tipos:

- Radiación atrapada en la magnetosfera (cinturones de radiación Van Allen): partículas procedentes del sol, atrapadas en el campo magnético terrestre. Debido a la asimetría del campo magnético terrestre, la radiación de los cinturones se distribuye de forma irregular. Su densidad está influenciada por las llamas solares, incrementándose mucho en caso de tormentas solares.

- Radiación cósmica: rayos cósmicos galácticos procedentes de fuera del sistema solar, tienen uno de sus orígenes en las explosiones de supernovas.

- Radiación solar: partículas energéticas solares procedentes del campo magnético del sol.

Radiación espacial. Fuente: nasa.gov

Efectos de la radiación en las FPGAs. Tipos de errores

Todos los chips de silicio son susceptibles a los efectos de la radiación, tanto ionizante como no ionizante. Se crean pares electrón-hueco en las estructuras MOS, por lo que la corriente de pérdidas aumenta y la tensión umbral del transistor varía. Pueden clasificarse en dos grandes grupos: efectos acumulativos y efectos singulares.

- Acumulativos: la dosis Total de Ionización o TID (Total Ionizing Dose) se produce por el incremento gradual de cargas atrapadas y defectos que son generados por procesos de ionización durante la exposición a la radiación, y que se acumulan principalmente en las capas dieléctricas de los dispositivos. Para el caso concreto de transistores MOS, la TID provoca variaciones de la tensión umbral y una disminución de la movilidad en el canal de conducción, junto con un incremento de la corriente de fugas entre drenador y fuente en la región de corte del transistor. Este efecto no produce errores inmediatos, pero una exposición prolongada -por su efecto acumulativo- envejece y daña el dispositivo electrónico, delimitando así la vida útil del mismo.

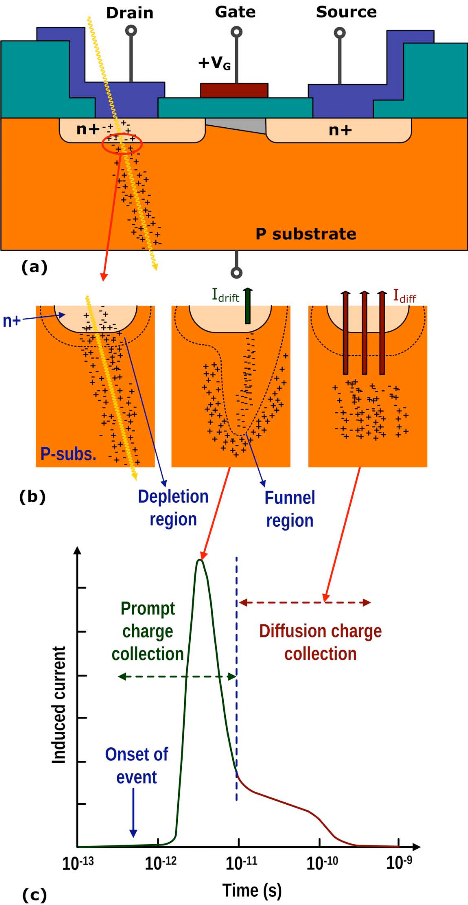

- Efectos singulares (Single Event Effects, SEEs): son causados por una única partícula ionizante que, al atravesar una determinada región sensible del dispositivo, crea una carga inducida que puede afectar de forma inmediata y temporalmente a su correcto funcionamiento o incluso llegar a destruir el mismo. Este artículo se centra únicamente en los efectos singulares SEE.

Los SEE se dividen en permanentes o destructivos (hard errors) y reversibles o no destructivos (soft errors), estos últimos son corregibles mediante diversas técnicas.

SEE (Single Event Effects) permanentes o destructivos (hard errors):

- SEGR (Single Event Gate Rupture) y SEB (Single Event Induced Burnout): ambos son producidos por una corriente alta inducida por la partícula de radiación. En el SEGR el resultado es la rotura de una puerta lógica, y en el SEB una parte del circuito.

- SEL (Single Event Induced Latchup): se crea una estructura parásita similar a un rectificador controlado de silicio (SCR), permitiendo la circulación de corrientes elevadas que pueden producir daños permanentes. Dependiendo del caso, puede producir daños instantáneos o producirlos con el paso del tiempo. Definido como destructivo pero corregible al dejar de alimentar el circuito si no se excede un límite de intensidad de corriente marcado.

SEE (Single Event Effects) reversibles o no destructivos (soft errors):

- SEU (Single Event Upsets): producidos por una partícula de radiación que afecta a un dato de la memoria. Un bit de datos de memoria invierte su valor lógico (de ‘0’ a ‘1’ o de ‘1’ a ‘0’) si la carga de la partícula supera la carga crítica del dispositivo.

- MBU (Multiple Bit Upsets): SEU que afecta a más de un dato de memoria.

- SET (Single Event Transient): producido por un voltaje alto inducido por la partícula de radiación. Causa un error en el bit de un circuito combinacional, propagándose a lo largo del circuito. Se considera un SEU en caso de afectar al bit de un circuito secuencial.

- SEFI (Single Event Functional Interrupt): caso particular de SEU que produce una variación en la funcionalidad básica o esencial del dispositivo.

Generación y transporte de cargas por efecto de un SEE en la región de drenador de un transistor NMOS. Fuente: [3].

Diferentes tecnologías FPGA. Relación con los SEE y reconfigurabilidad

El proceso de selección de FPGAs para aplicaciones espaciales tiene en cuenta dos grandes factores: la inmunidad a los SEE y la versatilidad del sistema (posibilidad de reconfiguración).

En función de la tecnología empleada por la FPGA para llevar a cabo su función de configuración se distinguen tres tipos de FPGAs:

- Antifuse: usan celdas de configuración de tecnología Antifusible desarrollada por Actel (para su familia de lógica programable). Son programadas una vez (one-time programmable, OTP), mantienen su valor de forma permanente y no hay vuelta atrás una vez son programadas. Se definen como no-volátiles, lo cual significa que las FPGA implementadas usando esta tecnología son "instant on" y no requieren de fuentes de configuración externas.

- Flash: usan celdas de configuración de tecnología Flash que se vuelca automáticamente en las células de configuración SRAM tras el inicio y/o reinicio. También son "instan on", no requiriendo fuentes de configuración externas. Son no-volátiles y re-programables un número limitado de veces. Las celdas de memoria flash tienen una inmunidad alta frente a los SEE.

- SRAM: usan celdas de configuración de tecnología SRAM para el almacenamiento de los datos de configuración. Son altamente re-programables, pero volátiles. Su coste es más reducido en relación a otros tipos de FPGAs pero requieren de una memoria no-volátil externa para su configuración tras su encendido o reinicio. Son susceptibles a los SEEs, dado que se basan en memoria estática.

Tipos de FPGA según la tecnología de almacenamiento de datos de configuración

Tipo de FPGA | Basada en Antifuse | Basada en SRAM | Basada en Flash |

Reconfigurable | No | Sí | Sí |

Volátil | No | Sí | No |

Inmunidad a SEE | Muy alta | Baja | Media-alta |

Coste | Muy alto | Medio | Alto |

Las FPGAs basadas en tecnología Antifuse han sido y son muy usadas en aplicaciones espaciales debido a la alta inmunidad frente a SEEs. Sin embargo, dada su no reconfigurabilidad, cada vez más aplicaciones espaciales utilizan FPGAs basadas en otras tecnologías. Las aplicaciones espaciales que utilizan FPGAs basadas en tecnología Flash son soluciones más recientes a las basadas en tecnología antifuse, pero con buenos resultados debido a la relación entre su resistencia a los SEEs y su capacidad de reconfiguración. Suelen ser sistemas cuya fabricación implementa un blindaje extra frente a la radiación. Las FPGAs basadas en Antifusible y Flash requieren de procesos adicionales además del proceso CMOS para crear el resto del chip, mientras que, las FPGAs basadas en tecnología SRAM son fabricadas utilizando el mismo proceso CMOS que el resto del chip, cuentan con una capacidad de reconfiguración casi ilimitada y un mayor rendimiento, debido a que suelen estar una o dos generaciones por delante de las tecnologías Flash y Antifusible, además de un coste más reducido que las basadas en tecnologías Flash y Antifusible. Como contrapartida, estas soluciones basadas en SRAM deben implementar un sistema de configuración externo con una memoria de tipo Flash o EEPROM para almacenar los ficheros usados en la reprogramación de la FPGA y poseen un consumo de energía más elevado.

La tecnología de proceso de fabricación FPGA, que determina el tamaño de la estructura del transistor, afecta al grado de tolerancia a la radiación: FPGAs fabricadas con procesos de 40nm o inferiores, presentan una mejora en la tolerancia a la radiación.

Seleccionar el mejor dispositivo FPGA para una tarea o conjunto de tareas concretas puede ser complicado porque existen muchas familias, y cada una ofrece diferentes recursos, rendimientos, tolerancias, interfaces y herramientas de desarrollo.

Técnicas de mitigación de errores producidos por efectos de radiación

Los efectos causados por las radiaciones en las FPGAs basadas en SRAM, debido a su susceptibilidad a los SEEs, implicó que -durante un tiempo- dicha tecnología se considerara inadecuada para aplicaciones aeroespaciales y espaciales. Actualmente, se emplean procesos de fabricación (que permiten tener FPGAs de 20nm) y técnicas de mitigación, con el resultado que FPGAs de tecnología SRAM se encuentran en sistemas como el Mars Curiosity Rover.

Las siguientes técnicas de mitigación de errores, o un conjunto de las mismas, son implementadas en los desarrollos FPGA para aplicaciones espaciales:

Técnicas Hardware de mitigación de SEE

- Blindaje hardware frente a radiación

- Técnicas de doble o triple redundancia

Técnicas Software de mitigación de SEE

- Depuración de datos de configuración (Configuration Scrubbing)

- Códigos de detección y corrección de errores y paridad

- Punto de verificación y recuperación (Checkpointing and Rollback Recovery)

- Redundancia temporal

- Codificación específica de las máquinas de estados

Sin embargo, implementaciones y desarrollos basados en FPGA no son una tarea fácil y es posible que no siempre tenga la experiencia, los recursos o el tiempo para cumplir con su planificación.

Nuestro equipo de ingenieros especializados en FPGAs y SoC / MPSoC te ofrece experiencia y servicios para desarrollar tu producto, con la misión de ayudarte a reducir tus ciclos de desarrollo. En GENERA Tecnologías tenemos una larga trayectoria ayudando a nuestros clientes a convertir la señal adquirida por el sensor en información procesada, confiable, en tiempo-real y en la menor latencia, para una amplia gama de aplicaciones y sectores. Contáctanos.

Referencias

[1] Radiation Impacts on Satellites due to GCRs and SEPs.

Mike Xapsos GSFC, Code 561, NASA.

https://ccmc.gsfc.nasa.gov/RoR_WWW/SWREDI/training-for-engineers/Xapsos_Space_Weather_Training_GSFC.pdf

[2] SEU Mitigation Techniques for Advanced Reprogrammable FPGA in Space.

Department of Computer Science and Engineering - CHALMERS UNIVERSITY OF TECHNOLOGY Gothenburg, Sweden, FREDRIK BROSSER, EMIL MILH.

http://publications.lib.chalmers.se/records/fulltext/202966/202966.pdf

[3] DISEÑO CMOS DE SISTEMAS DE FRONT-END PARA INSTRUMENTACIÓN AMBIENTAL EN MARTE.

Dpto. de Electrónica y Electromagnetismo – Facultad de Física Instituto de Microelectrónica de Sevilla, UNIVERSIDAD DE SEVILLA – CSIC.

https://idus.us.es/handle/11441/52295

[4] FAULT MANAGEMENT TECHNIQUES FOR SYSTEMS WITH SRAM-BASED FPGAS.

Universidad Politécnica de Madrid - Escuela Técnica Superior de Ingenieros de Telecomunicación.

http://oa.upm.es/37901/1/IGNACIO_HERRERA_ALZU_01.pdf

[5] High-Reliability FPGA-Based Systems: Space, High-Energy Physics, and Beyond. IEEE.

https://ieeexplore.ieee.org/document/7086415

Mike Xapsos GSFC, Code 561, NASA.

https://ccmc.gsfc.nasa.gov/RoR_WWW/SWREDI/training-for-engineers/Xapsos_Space_Weather_Training_GSFC.pdf

[2] SEU Mitigation Techniques for Advanced Reprogrammable FPGA in Space.

Department of Computer Science and Engineering - CHALMERS UNIVERSITY OF TECHNOLOGY Gothenburg, Sweden, FREDRIK BROSSER, EMIL MILH.

http://publications.lib.chalmers.se/records/fulltext/202966/202966.pdf

[3] DISEÑO CMOS DE SISTEMAS DE FRONT-END PARA INSTRUMENTACIÓN AMBIENTAL EN MARTE.

Dpto. de Electrónica y Electromagnetismo – Facultad de Física Instituto de Microelectrónica de Sevilla, UNIVERSIDAD DE SEVILLA – CSIC.

https://idus.us.es/handle/11441/52295

[4] FAULT MANAGEMENT TECHNIQUES FOR SYSTEMS WITH SRAM-BASED FPGAS.

Universidad Politécnica de Madrid - Escuela Técnica Superior de Ingenieros de Telecomunicación.

http://oa.upm.es/37901/1/IGNACIO_HERRERA_ALZU_01.pdf

[5] High-Reliability FPGA-Based Systems: Space, High-Energy Physics, and Beyond. IEEE.

https://ieeexplore.ieee.org/document/7086415

[6] Fuentes propias Genera Tecnologías.